System On Modules

| Product | Model | Description | Type | Price | Details |

|---|---|---|---|---|---|

| i.MX8M | iW-RainboW-G27M i.MX8M SMARC System On Module | SMARC | $Call | View |

| i.MX8 | iW-RainboW-G27M i.MX8 SMARC SOM | SMARC | $Call | View |

| 820 SMARC | iW-RainboW-G25M Snapdragon 820 SMARC System On Module | SMARC | $Call | View |

| RZ/G1H | iW-RainboW-G21M-Q7 RZ/G1H Qseven System On Module | Qseven | $Call | View |

| RZ/G1M G1N | iW-RainboW-G20M-Q7 RZ/G1M,G1N Qseven System On Module | Qseven | $Call | View |

| i.MX6 | iW-RainboW-G15M-Q7 i.MX6 Qseven System On Module | Qseven | $Call | View |

| Cyclone V | iW-RainboW-G17M-Q7 Cyclone V SoC System On Module | Qseven/FPGA | $Call | View |

| DM8168 | iW-RainboW-G12M-Q7 DaVinci DM8168 Qseven SOM | Qseven | $Call | View |

| i.MX51 | iW-RainboW G8M-Q7 i.MX51 Qseven System On Module | Qseven | $Call | View |

| Zynq 7000 | iW-RainboW-G28M Zynq 7000 SoC / FPGA System On Module | SODIMM/FPGA | $Call | View |

| RZ/G1E | iW-RainboW-G22M-SM RZ/G1E SODIMM System On Module | SODIMM | $Call | View |

| i.MX6ULL | iW-RainboW-G18M-SM i.MX6ULL SODIMM System On Module | SODIMM | $Call | View |

| i.MX6 Ultra | iW-RainboW-G18M-SM i.MX6 Ultra Lite SODIMM System On Module | SODIMM | $Call | View |

| i.MX6 | iW-RainboW-G15M-SM i.MX6 SODIMM System On Module | SODIMM | $Call | View |

| i.MX6UL | iW-RainboW-G18D i.MX6UL SODIMM Development Platform | SODIMM | $Call | View |

| Zynq | iW-RainboW-G30M Zynq UltraScale+ SoC / FPGA System On Module | FPGA | $Call | View |

| Arria 10 SoC | iW-RainboW-G24M Arria 10 SoC / FPGA System On Module | FPGA | $Call | View |

| Vybrid VF6xx | iW-RainboW-G16M-µMXM Vybrid VF6xx / VF5xx µMXM SO | Custom | $Call | View |

| i.MX6 MXM | iW-RainboW-G15M-MXM i.MX6 MXM System On Module | Custom | $Call | View |

| i.MX53 MXM | RainboW-G11M-MXM i.MX53 MXM System On Module | Custom | $Call | View |

| Atom Z5xx | RainboW-G6M-Q7 Atom Z5xx Qseven SOM | Legacy | $Call | View |

| i.MX51 | i.MX51 System On Module | Legacy | $Call | View |

| i.MX27 | iW-RainboW-G3 i.MX27 System On Module | Legacy | $Call | View |

| PPC MPC 864x | iW-RainboW-G9M PPC MPC 864x XMC / PrPMC | Legacy | $Call | View |

| FPGA Radar | RainboW-G14M FPGA Radar Interface Card | Legacy | Legacy | View |

Development Platforms

| Product | Model | Description | Type | Price | Details |

|---|---|---|---|---|---|

| Snapdragon | iW-RainboW-G25D Snapdragon 820 SMARC Development Kit | SMARC | $Call | View |

| RZ/G1H | iW-RainboW-G21D-Qseven RZ/G1H Qseven Development Kit | Qseven | $Call | View |

| RZ/G1M,G1N | iW-RainboW-G20D-Qseven RZ/G1M,G1N Qseven Development Platform | Qseven | $Call | View |

| i.MX6 | i.MX6 Qseven Development Platform | Qseven | $Call | View |

| Altera | Altera Cyclone V SoC Development Platform | Qseven | $Call | View |

| i.MX51 | i.MX51 Qseven Development Kit | Qseven | $Call | View |

| DM8168 | DM8168 Qseven Development Platform | Qseven | $Call | View |

| i.MX6ULL | iW-RainboW-G18D i.MX6ULL SODIMM Development Platform | SODIMM | $Call | View |

| RZ/G1E | iW-RainboW-G22D-SODIMM RZ/G1E SODIMM Development Platform | SODIMM | $Call | View |

| i.MX6UL | iW-RainboW-G18D i.MX6UL SODIMM Development Platform | SODIMM | $Call | View |

| Arria 10 SoC | iW-RainboW-G24D Arria 10 SoC FPGA Development Platform | FPGA/Custom | $Call | View |

| Altera Cyclo | iW-RainboW-G17D Altera Cyclone V SoC Development Platform | FPGA | $Call | View |

| Vybrid uMXM | iW-RainboW-G16D Vybrid uMXM Development Platform | Custom | $Call | View |

| i.MX6 MXM | i.MX6 MXM Development Platform | Custom | $Call | View |

| i.MX53 MXM | iW-RainboW-G11D i.MX53 MXM Development Kit | Custom | $Call | View |

| Atom Z5xx | iW-RainboW-G6D Atom Z5xx Development Platform | Legacy | $Call | View |

| i.MX51 | iW-RainboW-G8D i.MX51 Development Kit | Legacy | $Call | View |

| PXA 270 | iW-RainboW-G4D PXA 270 Development Kit | Legacy | $Call | View |

Single Board Computers

| Product | Model | Description | Type | Price | Details |

|---|---|---|---|---|---|

| RZ/G1C | iW-RainboW-G23S RZ/G1C Single Board Computer | Single Board | $Call | View |

| Snapdragon | iW-RainboW-G25S Snapdragon 820 SBC | Single Board | $Call | View |

| Single Board | iW-RainboW-G15S Single Board Computer i.MX6 Pico ITX | Single Board | $Call | View |

| RZ/G1E | iW-RainboW-G22S RZ/G1E Single Board Computer | Single Board | $Call | View |

| Vybrid Pico | iW-RainboW-G16S Vybrid Pico ITX SBC | Single Board | $Call | View |

| i.MX50 QSB | RainboW-G13S i.MX50 QSB | Single Board | $Call | View |

| i.MX27 SBC | RainboW-G3V i.MX27 SBC | Single Board | $Call | View |

Board Support Packages

| Product | Model | Description | Type | Price | Details |

|---|---|---|---|---|---|

| Pico ITX SBC | Windows Embedded Compact 7 on i.MX6 Pico ITX SBC | Board Support | $Call | View |

| SABRE SDP/SD | Windows Embedded Compact 7 on i.MX6 SABRE SDP/SDB | Board Support | $Call | View |

| Rainbow G15D | Windows Embedded Compact 7 on i.MX6 Rainbow G15D | Board Support | $Call | View |

| Rainbow G11D | Windows Embedded Compact 7 on i.MX53 Rainbow G11D | Board Support | $Call | View |

Product Solutions

| Product | Model | Description | Type | Price | Details |

|---|---|---|---|---|---|

| HMI Solution | HMI Solution | Product | $Call | View |

| OBD II | iW-RainboW-G26 Connected Car Device - OBD II | Product | $Call | View |

| eYe | Wi-Fi enabled PLC system eYe - enhance Your efficiency | Product | $Call | View |

| i.MX6 Based | i.MX6 Based Digital Signage Solution | Product | $Call | View |

| Handheld | iW-RainboW-G29 Rugged Handheld Computer | Product | $Call | View |

| POC-Car PC | POC-Car PC | Product | $Call | View |

| Videophone | POC-Videophone | Product | $Call | View |

| Camera | POC- Rear View Camera | Product | $Call | View |

FPGA IP Cores

| Product | Model | Description | Type | Price | Details |

|---|---|---|---|---|---|

| 80186EC | 80186EC Processor | Processor | $Call | View |

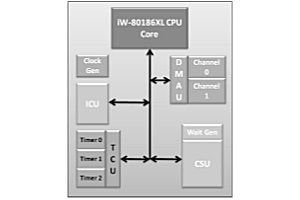

| 80186XL | 80186XL Processor | Processor | $Call | View |

| 80188XL | 80188XL Processor | Processor | $Call | View |

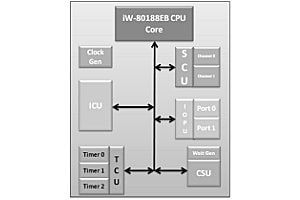

| 80188EB | 80188EB Processor | Processor | $Call | View |

| 8237 DMA | 8237 DMA Controller | Peripheral | $Call | View |

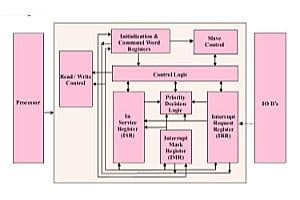

| 8259A | 8259A Interrupt Controller | Peripheral | $Call | View |

| 8254 | 8254 Programmable Timer | Peripheral | $Call | View |

| 8251 Serial | 8251 Serial Controller | Peripheral | $Call | View |

| 8530 Multi | 8530 Multi-Protocol Controller | Peripheral | $Call | View |

| SATA Host | SATA Host Controller | Storage | $Call | View |

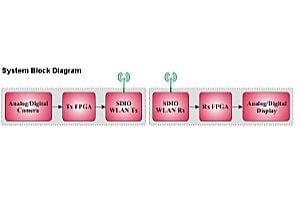

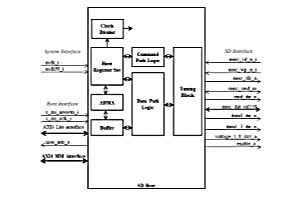

| SD/SDIO Host | SD / SDIO Host Controller 3.0 | Storage | $Call | View |

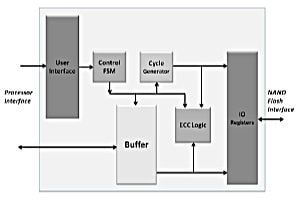

| NAND Flash | NAND Flash Controller | Storage | $Call | View |

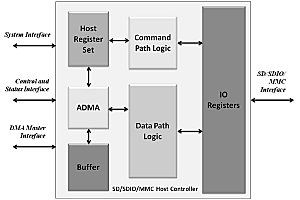

| SD/SDIO/MMC | SD / SDIO / MMC Host Controller | Storage | $Call | View |

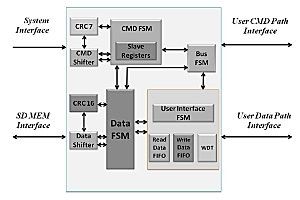

| SD Memory | SD Memory Slave Controller | Storage | $Call | View |

| SDIO Slave | SDIO Slave Controller | Storage | $Call | View |

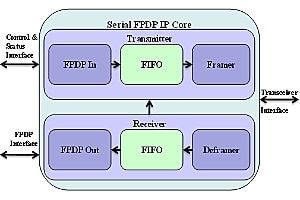

| Serial FPDP | Serial FPDP (sFPDP) | Interface | $Call | View |

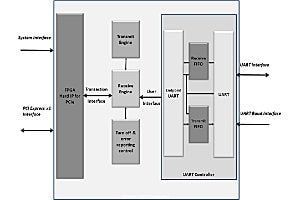

| SDIO to UART | SDIO to UART Controller | Interface | $Call | View |

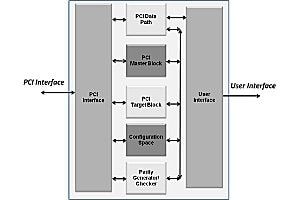

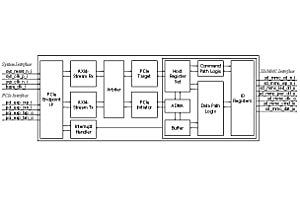

| PCI Control | PCI Controller | Interface | $Call | View |

| PCIe to UART | PCIe to UART Bridge | Interface | $Call | View |

| PCIe-ISA | PCIe-ISA Bridge | Interface | $Call | View |

| PCIe to SD | PCIe to SD/MMC Bridge | Interface | $Call | View |

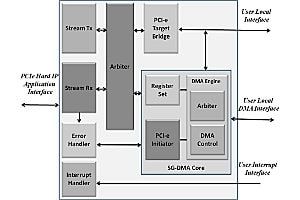

| DMA Core | DMA Core for PCIe Hard IP | Interface | $Call | View |

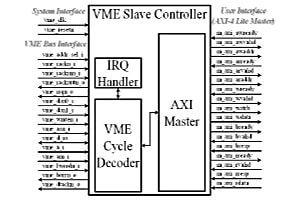

| VME Slave IP | VME Slave IP Core (VME to AXI Bus Bridge) | Interface | $Call | View |

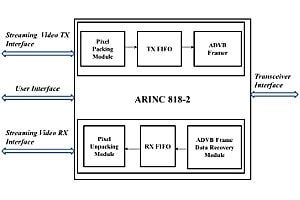

| ARINC 818-2 | ARINC 818-2 IP Core | Video | $Call | View |

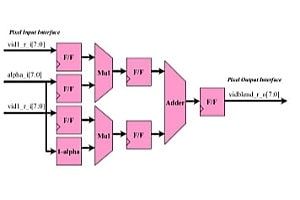

| Alpha Blend | Alpha Blender | Video | $Call | View |

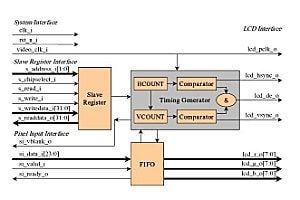

| LCD/HDMI | LCD/HDMI Video Output Interface | Video | $Call | View |

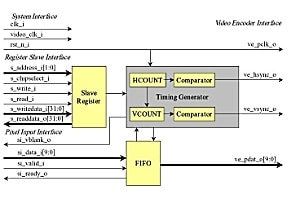

| Video Encode | Video Encoder Interface | Video | $Call | View |

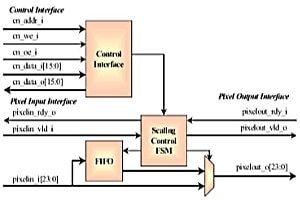

| Video Scaler | Video Scaler | Video | $Call | View |

| Chroma | Chroma Resampler | Video | $Call | View |

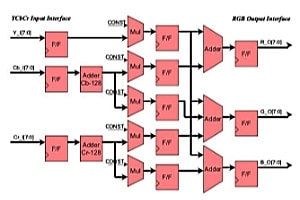

| Color Space | Color Space Conversion | Video | $Call | View |

| DeInterlacer | Video DeInterlacer | Video | $Call | View |

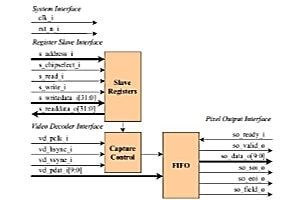

| Decoder | Video Decoder Interface | Video | $Call | View |

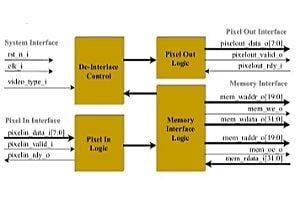

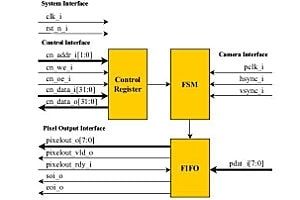

| Camera/HDMI | Camera/HDMI Video Input Interface | Video | $Call | View |

| FMC Add-On | FMC Add-On Cards | FMC Add-On | $Call | View |